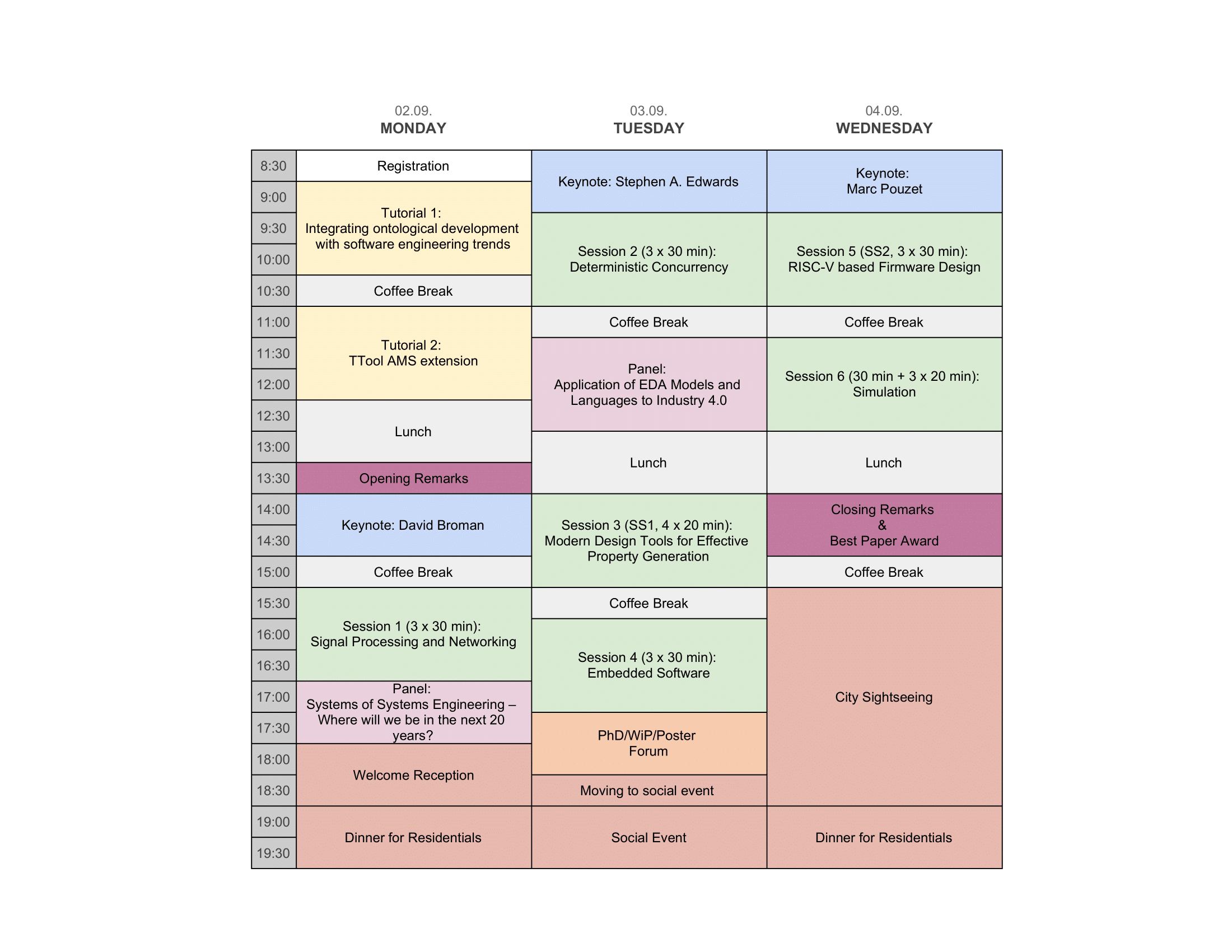

You can view or download the program flyer here (PDF)

| Session | Authors | Title |

|---|---|---|

| Session 1 | Chair: Julio Medina | Universidad de Cantabria, ES |

| 1 | George Ungureanu, Timmy Sundström, Anders Åhlander, Ingo Sander and Ingemar Söderquist |

Formal Design, Co-Simulation and Validation of a Radar Signal Processing System**** |

| 2 | Muhammad Hassan, Daniel Grosse, Thilo Voertler, Karsten Einwich and Rolf Drechsler |

Functional Coverage-Driven Characterization of RF Amplifiers*** |

| 3 | Jie Hou and Martin Radetzki | A methodology to compute long-term fault resilience of NoCs under fault-tolerant routing algorithms |

| Session 2 | Chair: Stephen Edwards | Columbia University, USA |

| 1 | Edward A. Lee and Marten Lohstroh | Deterministic Actors |

| 2 | Alain Girault, Nicolas Hili, Eric Jenn and Eugene Yip | A Multi-Rate Precision Timed Programming Language for Multi-Cores |

| 3 | Alexander Schulz-Rosengarten, Steven Smyth and Michael Mendler | Towards Object-Oriented Modeling in SCCharts |

| Session 3 | Chair: Heinz Riener | EPFL, CH |

| 1 | Gianluca Martino and Goerschwin Fey | Syntax-Guided Enumeration of Temporal Properties |

| 2 | Heinz Riener | Exact synthesis of LTL properties from traces |

| 3 | Tara Ghasempouri, Alessandro Danese, Graziano Pravadelli, Nicola Bombieri and Jaan Raik |

RTL assertion mining with automated RTL to-TLM abstraction |

| 4 | Oliver Keszocze and Ian Harris | Chatbot-based assertion generation from natural language specifications |

| Session 4 | Chair: Eugene Yip | University of Bamberg, DE |

| 1 | Lukas Gressl, Christian Steger and Ulrich Neffe | Security Driven Design Space Exploration for Embedded Systems |

| 2 | Manuel Strobel and Martin Radetzki | A Backend Tool for the Integration of Memory Optimizations into Embedded Software |

| 3 | Friederike Bruns, Kim Gruettner and Philipp Ittershagen | Time Measurement and Control Blocks for Bare-Metal C++ Applications |

| Session 5 | Chair: Daniel Große | DFKI GmbH, DE |

| 1 | Christoph Gerum, Alexander Jung, Joscha-Joel Benz, Oliver Bringmann | A Context-sensitive Timing Model for Automated Firmware Generation onto RISC-V-based Microprocessor Platforms |

| 2 | Vladimir Herdt, Daniel Große, Rolf Drechsler | Firmware Verification trough Concolic Testing for RISC-V Systems |

| 3 | Michael Schwarz, Dominik Stoffel, Wolfgang Kunz | Checking for Peripheral Device Side Effects in Firmware Variants |

| Session 6 | Chair: Carna Zivkovic | TU Kaiserslautern, DE |

| 1 | Simone Caligola, Tommaso Carlucci, Franco Fummi, Carlo Laudanna, Gabriela Constantin, Nicola Bombieri and Rosalba Giugno |

Efficient Simulation and Parametrization of Stochastic Petri Nets in SystemC: A Case study from Systems Biology*** |

| 2 | Stefano Spellini, Roberta Chirico, Michele Lora and Franco Fummi | Languages and Formalisms to Enable EDA Techniques in the Context of Industry 4.0 |

| 3 | Gines Domenech-Asensi and Tom Kazmierski | Simulation acceleration of image filtering on CMOS vision chips using many-core processors |

| 4 | Giovanni Liboni and Julien Deani | WIP on ordination Language to Automate the Generation of Co-Simulations |

| PhD/WiP/Poster Session | Chair: Terrence Mak | University of Southampton, GB |

| PhD/WiP/Poster Forum | Stefano Spellini | Enabling Design Automation Techniques in the Context of Industry 4.0: Languages and Formalisms |

| PhD/WiP/Poster Forum | Simone Caligola | Modeling and Simulation of Metabolic Networks through SystemC language |

| PhD/WiP/Poster Forum | Rafael Angel Gutierrez Nuno | A Phase Lag Index Hardware Calculation for Real-time Electroencephalography Studies |

| PhD/WiP/Poster Forum | Michail Pligouroudis | FPGA-based Multicore Acceleration for Sparce Matrix Vector Multiplication |

| Speakers in bold | *** Best Paper Candidates **** Best Paper Winner |

Systems of Systems Engineering – Where will we be in the next 20 years?

Abstract:

As engineered systems become more and more complex, challenges and issues, the current system engineering practices face with, get higher. Characterizing and designing such systems and their interactions is not an easy task and it must involve interdisciplinary methods and disciplines that need to ensure that all system aspects are covered and integrated. A new challenge that arises with the complexity of modern systems is the huge amount of data we need to deal with. This encourages the involvement of new tools and methods such as system analysis and smart decision making based on ML and AI methods. This panel session brings senior engineers and scientists from several SE disciplines to discuss current issues and challenges they face with.The panel will facilitate an open discussion how they see the evolvement of SE in the future: Will smart algorithms help a system learn from its failures and make a better version of itself without human interactions?

Panelist: Alain Girault (alain.girault@inria.fr), INRIA, Grenoble Edward Lee (eal@berkeley.edu), University of California Berkeley Scott Walker (sjiw@soton.ac.uk), University Southampton Moderator: Carna Zivkovic (zivkovic@cs.uni-kl.de), TU Kaiserslautern

Application of EDA Models and Languages to Industry 4.0

Abstract:

The term Industry 4.0 was born in 2011 at the Hannover Fair in Germany as a vision of “smart factory” in which all machines are connected to one another and manufacturing processes are automated to shorten time-to-market, reduce costs and provide high quality products. However, the deployment of Industry 4.0 has its own price; dealing with numerous challenges is required to deploy and realize such complex solution. And this is the point where we come to Modeling as one of key enablers for structuring and understanding the complexity of systems and processes in early development phases. The goal of this panel to discuss and try to provide answers to the following key questions:

David Broman

KTH Royal Institute of Technology, SE

Abstract:

Designing a new programming or modeling language is a challenging enterprise that requires both large amount of time and effort, as well as significant knowledge in programming language theory and compilers. As a consequence, during the past decades, significant amount of research has been done in the area of embedding languages into other host languages, and to construct various platforms for compiler construction. However, although significant progress in the area, fundamental challenges remain, including i) the ability to easily compose different language fragments in a sound manner to generate new languages, ii) to enable good error messages and to not leak abstractions from host languages, and iii) to automatically generate as good compilers and execution environments as if the language environments were constructed from scratch. In this talk, I will give an overview of our ongoing project of designing an new framework for creating domain-specific languages. In particular, I will describe and discuss the key design objectives and key components of this project, including i) heterogeneous composition of language fragments for designing domain-specific modeling languages, ii) the effort of creating a self-learning model compiler infrastructure that can learn from examples, and iii) efficient target compilation strategies, both for online real-time computation and offline batch processing. The work will be discussed from the context of different domain-specific languages, including a core language for probabilistic programming, and a domain-specific modeling language for equation-based modeling and simulation of complex physical systems.

Bio:

David Broman is an Associate Professor at the KTH Royal Institute of Technology in Sweden, where he is leading the Model-based Computing Systems (MCS) research group. Between 2012 and 2014, he was a visiting scholar at the University of California, Berkeley, where he also was employed as a part time researcher until 2016. David received his Ph.D. in Computer Science in 2010 from Linköping University, Sweden, and was appointed Assistant Professor there in 2011. He earned a Docent degree in Computer Science in 2015. His research focuses on model-based design of time-aware systems, including cyber-physical systems, embedded systems, and real-time systems. In particular, he is interested in programming and modeling language theory, formal semantics, compilers, and machine learning. David has received an outstanding paper award at RTAS (co-authored 2018), a best paper award in the journal Software & Systems Modeling (SoSyM award 2018), the award as teacher of the year, selected by the student union at the KTH Royal Institute of Technology (2017), the best paper award at IoTDI (co-authored 2017), awarded the Swedish Foundation for Strategic Research's individual grant for future research leaders (2016), and the best paper presentation award at CSSE&T (2010). He has worked several years within the software industry, co-founded four companies, co-founded the EOOLT workshop series, and is a member of IFIP WG 2.4, Modelica Association, and a senior member of IEEE.

- Web page: David Broman

Stephen A. Edwards

Columbia University, USA

Abstract:

Designing an effective language requires you to strike a delicate balance between what is possible, consistent, implementable, and understandable. Like LEGOs, all the pieces need to fit together seamlessly, but unlike LEGOs, a crucial goal is to enable the user to make new, even more powerful blocks. And all of this needs to be done while considering whether everything has a clear, unambiguous meaning and implemented efficiently with available resources. In this talk, I'll describe a variety of successful languages and how they managed (or failed) at this delicate balancing act.

Bio:

Stephen A. Edwards received the B.S. degree in Electrical Engineering from the California Institute of Technology in 1992, and the M.S. and Ph.D degrees, also in Electrical Engineering, from the University of California, Berkeley in 1994 and 1997 respectively. He is currently an associate professor in the Computer Science Department of Columbia University in New York, which he joined in 2001 after a three-year stint with Synopsys, Inc., in Mountain View, California. His research interests include embedded system design, domain-specific languages,compilers, and high-level synthesis.

Marc Pouzet

École normale supérieure, FR

Abstract:

SCADE is a high-level language and environment for developing safety-critical embedded control software. It has been used for more than twenty years in various application domains like avionics, nuclear plants, transportation, and automotive. SCADE was founded on the synchronous data-flow language Lustre invented by Caspi and Halbwachs. In the early years, it was mainly seen as a graphical notation for Lustre but with the unique and key addition of a code generator qualified to the highest standards for safety-critical applications. In 2008, a major revision based on the new language `Scade 6' was released. This language is an original combination of the Lustre data-flow style with control structures borrowed from Esterel and SyncCharts, with compilation and static analyses from Lucid Synchrone to ensure safety properties. This increase in expressiveness together with the qualified code generator have dramatically widened the scope of applications developed with SCADE. Scade 6 is now used for almost ten years. In this talk, we shall present the main design decision on the language. We illustrate the novel programming language constructs, the different static checks performed by the compiler and defined as dedicated type systems and the properties it ensures, how sequential code is generated and the overall compiler organisation to satisfy the qualification process. We also discuss several possible extensions of the language and its compilation for the future. One of these extensions is hybrid system modeling, as explored in the language Zelus; another extension is the generation of code for multi-core architectures.

Bio:

Marc Pouzet is professor in computer science at Ecole normale superieure in Paris, leader of the INRIA team PARKAS and Director of Studies at the CS department. His research topic is the design, semantics and implementation of programming languages for reactive system with compile-time guaranties of safety properties like determinacy and execution in bounded time and space. He has particular interest for synchronous languages, their extensions and their embedding into functional typed languages. He developed or was involved in several languages (e.g., Lucid Synchrone, ReactiveML), compilation techniques and analyses that are integrated in commercial tools, notably the language Scade 6 and its compiler, developed by ANSYS/Esterel-Technologies. His current activity focuses on the semantics and implementation of hybrid systems modelers (e.g., Simulink, Modelica), the design and implementation of Zelus, a synchronous language that mixes discrete and continuous time, and the formal certification of a Lustre compiler with Coq. He collaborated with several research and production team (Philips Natlas, NXP, Dassault-Systemes, Esterel-Technologies) and served as scientific advisor. His work received best paper awards in conferences on embedded software (EMSOFT, LCTES) and received with Louis Mandel, the award for the most influential PPDP'05 paper for the language ReactiveML. He have been junior member of Institut Universitaire de France from 2007 to 2012. In 2016, he received the innovation award by INRIA - French Academy of Sciences - Dassault-Systèmes.

Maria Poveda

Universidad Politécnica de Madrid, ES

Alba Fernandez Izquierdo

Universidad Politécnica de Madrid, ES

Abstract:

Ontologies are defined in Computer Science as formal, explicit specifications of shared conceptualisations. The discipline of Ontology Engineering can be understood as the one that works on methods, tools and techniques to facilitate the development of ontologies. This discipline has been active for over more than two decades, and has witnessed an important evolution during its lifetime. As ontologies are being increasingly adopted in information systems, the ontological engineering methodologies are moving from heavy-weight and traditional life-cycles to embrace agile and software development practices. In this context, some ontological engineering supporting tools are being developed to integrate and orchestrate activities that are usually carried out repeatedly during ontological engineering projects. This is the case for OnToology, an on-line application that exploits GitHub capabilities to ease collaborative ontology development focusing on ontology documentation, evaluation and publication. This tutorial will cover both methodological and technical aspects of collaborative ontology development. It will include practical activities that will be supported by OnToology in combination with other systems. At the end of the tutorial attendees would be able to carry out and adapt common ontology development activities by incorporating OnToology into their workflows. The examples used in the tutorial will be taken from the VICINITY ontology network. However, the participants can follow the tutorial activities applying the acquired knowledge to their own use cases.

Bio:

Dr. María Poveda-Villalón is a lecturer in the Artificial Intelligence Department of the Universidad Politécnica de Madrid and is also part of the Ontology Engineering Group research lab. Her research activities focus on Ontological Engineering, Ontology Evaluation, Knowledge Representation and the Semantic Web. Previously she finished her studies in Computer Science (2009) by Universidad Politécnica de Madrid, and then she moved to study the Artificial Intelligence Research Master finished in 2010 in the same university. She has worked in the context of Spanish research projects as well as in European projects such as ETSI STF for SAREF extensions, VICINITY (H2020-688467), READY4SmartCities (FP7-608711), and NeOn (FP6-027595). She has contributed to the organization of the "Linked Data in Architecture and Construction Workshop" since 2015 edition, the "13th OWL: Experiences and Directions Workshop and 5th OWL reasoner evaluation workshop" in 2016, the "Linked Energy Data Vocamp" in 2015 and the "Catching up with ontological engineering: To git-commit and beyond" tutorial at EKAW2018. Finally, she is part of the W3C Web of Things Working Group.

Alba Fernández Izquierdo is a Ph.D. Candidate in the Ontology Engineering Group (Universidad Politécnica de Madrid, Spain).

She received her Bachelor Degree in Computer Engineering from Universidad de Santiago de Compostela (Spain) in 2015 and her MSc Degree in Artificial Intelligence from Universidad Politécnica de Madrid (Spain) in 2016.

She is currently working on ontology testing through ontological requirements. She is focused on ontology quality and ontological collaborative engineering.

- Web page: Maria Poveda

- Web page: Alba Fernandez Izquierdo

Daniela Genius

Sorbonne Université - LIP6, FR

Abstract:

Embedded systems are commonly built upon heterogeneous digital and analog integrated circuits, including sensors and actuators. Model-driven approaches for designing software and hardware have been proposed, yet they are generally limited to the digital parts of systems. This tutorial for the verification and virtual prototyping of embedded systems. These systems are described at different abstraction levels, starting from a SysML-like high-level model down to software design and mapping, from which a cycle-bit accurate prototype is generated. This prototype is based on the SoCLib library of virtual components written in SystemC. In the second part of the tutorial we will show how TTool has been extended to model and simulate analog/mixed-signal systems, and how the simulation handles the resulting synchronization issues. Last but not least, demonstration will be performed on a rover, as a case study, which will first be modeled by a purely digital design, then the sensors’ models will be added and the SystemC-AMS part of the prototype for co-simulation with SoCLib will be generated.

Bio:

Daniela Genius is an assistant professor at Paris Sorbonne University and member of the "Embedded Systems" team at LIP6 laboratory in Paris, France.

She obtained her PhD in Karlsuhe, Germany in 2000, then spent six months as a PostDoctoral researcher at the University of Chapel Hill, North Carolina, before joining Philips Research France as a

PostDoctoral researcher during two years, in a project with INRIA, dealing with compilation issues for high resolution video processors.

Since 2002, she is assistant professor in the System on Chip department of LIP6. Her research interests are virtual prototyping for heterogeneous

MP-SoC, hardware/software co-design, and design space exploration for NoC-based multi-processor systems on chip.

- Web page: Daniela Genius