FDL TBA

Forum on specification & Design Languages

@TBA, TBA

TBA, TBA

You can download the FDL 2020 Proceedings here (.zip)

You can view or download the program flyer here (.pdf)

| Authors | Title | Type | Session |

|---|---|---|---|

| Saranya Natarajan (V) and David Broman | Temporal Property-Based Testing of Timed C using Time-Flow Graphs | Full Research Papers | 1 |

| Marten Lohstroh (V) , Christian Menard, Alexander Schulz-Rosengarten, Matthew Weber, Jeronimo Castrillon and Edward Lee | A Language for Deterministic Coordination Across Multiple Timelines ** | Full Research Papers | 1 |

| George Ungureanu (V) , Rodolfo Jordão and Ingo Sander | Exploiting Dataflow Models for Parallel Simulation of Discrete Timed Systems | Short Papers | 1 |

| Stephen A. Edwards (V) and John Hui | The Sparse Synchronous Model | Full Research Papers | 2 |

| Lena Grimm (P) , Steven Smyth, Alexander Schulz-Rosengarten, Reinhard von Hanxleden and Marc Pouzet | From Lustre to Graphical Models and SCCharts | Full Research Papers | 2 |

| Andreas Boysen (P) , Alexander Schulz-Rosengarten and Reinhard von Hanxleden | A Hard Real Time Demonstrator for Dynamic Ticks and Timed SCCharts | Full Research Papers | 2 |

| Aurélien Lamercerie (V) and Benoît Caillaud | An Algebra of Deterministic Propositional Acceptance Automata (DPAA) | Full Research Papers | 3 |

| Friedrich Gretz, Franz-Josef Grosch, Michael Mendler (P) and Stephan Scheele | Synchronized Shared Memory and Procedural Abstraction: Towards a Formal Semantics of Blech | Full Research Papers | 3 |

| Michel Reniers and Sander Thuijsman (P) | Supervisory Control for Dynamic Feature Configuration in Product Lines ** | Full Research Papers | 3 |

| Vladimir Herdt (V) , Daniel Grosse, Eyck Jentzsch and Rolf Drechsler | Efficient Cross-Level Testing for Processor Verification: A RISC-V Case-Study ** | Full Research Papers | 4 |

| Freek van den Berg (P) , Vaclav Camra, Martijn Hendriks, Marc Geilen, Petr Hnetynka, Fernando Manteca, Pablo Pedro Sanchez, Tomas Bures and Twan Basten | QRML: A Component Language and Toolset for Quality and Resource Management | Full Research Papers | 4 |

| Matthew Johns (V) and Tom Kazmierski | A Minimal RISC-V Vector Processor for Embedded Systems | Short Papers | 4 |

| Alexander Brauckmann (P) , Andrés Goens and Jeronimo Castrillon | ComPy-Learn: A toolbox for exploring machine learning representations for compilers | Special Session 1 | 5 |

| Hugh Leather (V) and Chris Cummins | Machine Learning in Compilers: Past, Present and Future | Special Session 1 | 5 |

| Xujie Si (V) | End-to-end Learning for Program Verification | Special Session 1 | 5 |

| Pavol Bielik (P) | Robust Models for Source Code: Techniques and Applications | Special Session 1 | 5 |

| François Pecheux (V) , Liliana Andrade, Marie-Minerve Louerat, Ilias Bournias, Roselyne Chotin and Daniela Genius | Virtual Prototyping of Open Source Heterogeneous Systems with an Open Source Framework Featuring SystemC MDVP Extensions | Special Session 2 | 6 |

| Wolfgang Scherr (V) and Karsten Einwich | Beyond real number modeling: Comparison of analog modeling approaches. | Special Session 2 | 6 |

| Frank Rethmeier (V) | Top-down design flow of an RF-to-bits receiver using SystemC-AMS | Special Session 2 | 6 |

| Debora Maria Short Sotero, Carna Zivkovic, Christoph Grimm (V) , Johannes Kölsch, Maximilian Ferstl, Dirk Denger, Daniel Krems and Andre Barisic | Bringing Uncertainties to System Simulation: A SystemC AMS Case Study | Special Session 2 | 6 |

| Marcel Christian Werner (P) and Klaus Schneider | Reengineering of Programmable Logic Controller Applications Using Imperative Synchronous Programming Language Quartz | PhD/Work in Progress Papers | PhD / WiP |

| Guillaume Baudart, Jean-Louis Colaço, Louis Mandel, Michael Mendler (P) and Marc Pouzet | WiP: A Co-Iterative Synchronous Interpreter | PhD/Work in Progress Papers | PhD / WiP |

| George Ungureanu (V) | ForSyDe-Atom: Design and Synthesis of Heterogeneous Embedded Systems | PhD/Work in Progress Papers | PhD / WiP |

| Mark Kettner (V) , Behnam Razi Perjikolaei and Wolfgang Nebel | WiP: Modelling neural networks as SDFG representations for energy efficient hardware | PhD/Work in Progress Papers | PhD / WiP |

| (V) = Virtual (P) = Physical Presenter | ** Best paper Candidate |

Abstract:

Cyberphysical Systems (CPS), combining physical devices and software

artifacts, are commonly found in many industries, in the aerospace,

automotive, railway and energy sectors. Their design involve

multi-disciplinary teams, working together both on the design of the

physics and of the software. This requires the modeling of the

dynamics of both physics and software. A major trend in industry, is

to build digital twins. They are executable models of a whole system,

on which a variety of analyzes and tests can be carried out, much

before a prototype of the actual system can be build. Hybrid

mathematical modeling languages such as Simulink, Modelica, or

System-C AMS are widely used to capture both the continuous-time

(physics) and the discrete-time (software) dynamics of cyber-physical

systems.

However, CPS requirements are much harder to formalize, because they

only provide a partial specification of the system's behavior, with

the consequence that models are non-deterministic, by essence, so that

the variability of the different designs can be captured in a single

model. Mathematical modeling languages such as Simulink or Modelica

are ill-suited to formalize requirements, for the basic reason that

they can cope only with deterministic behavior.

This panel will focus on the concepts, languages and tools, with which

CPS Requirements can be formalized and used for verification and

testing. Several practical approaches will be compared, namely: the

Modelica Requirements Library, the SpaceEx Hybrid Systems modeling and

verification tool, and Verilog & System-C AMS frameworks.

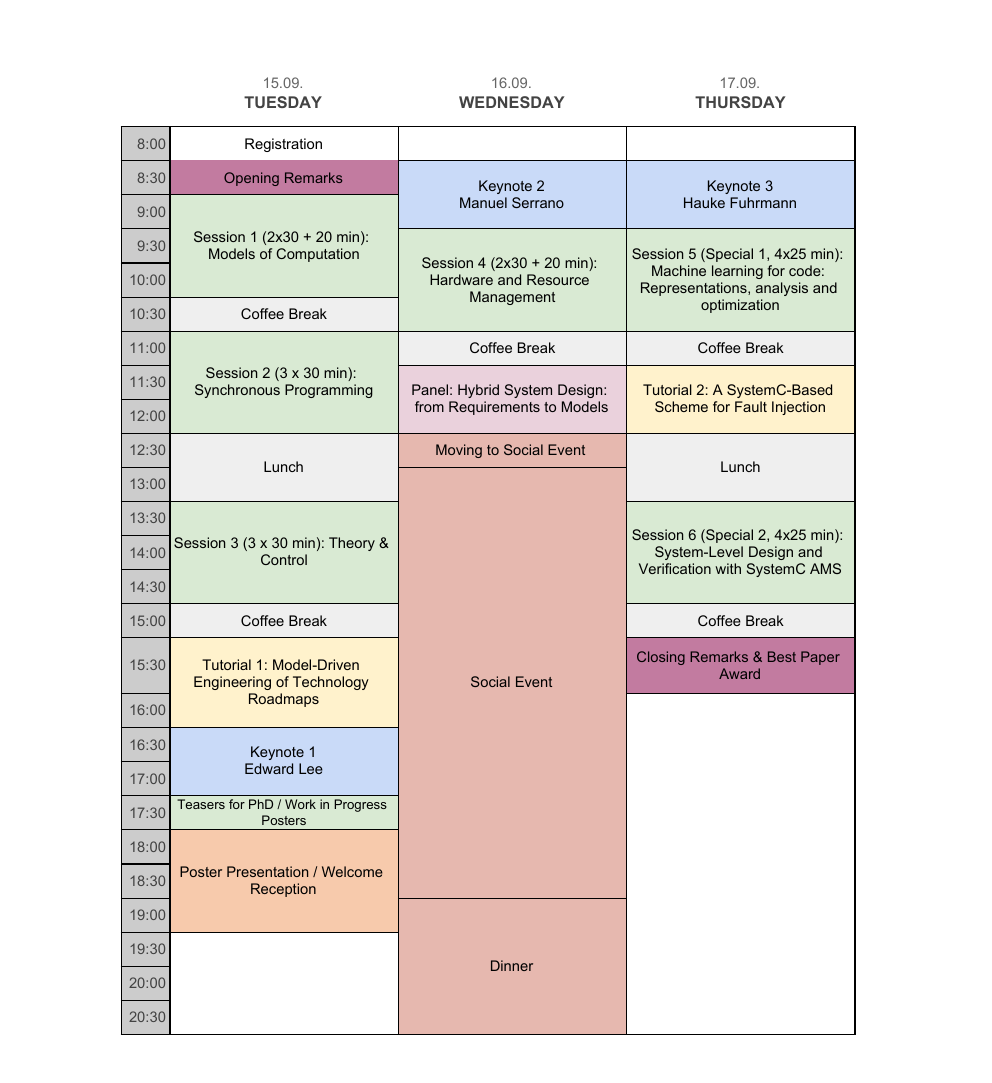

The social event will be a cruise aboard the historic schooner TWISTER , followed by an S&B Dinner kindly supported by Scheidt & Bachmann.

- 13:00: boarding “TWISTER” at Kiel-Blücherbrücke, return around 19:00

- 19:15: Dinner at “Schöne Aussichten”, Düsternbrooker Weg 16, 24105 Kiel